### Resumo

As empresas estão cada vez mais procurando um diferencial em seus negócios criando novos modelos de gestão e novos serviços para seus clientes, com isso ficou imprescindível o emprego de novas tecnologias tais como: sistemas embarcados, celulares e notebooks. Com o advento dessas novas demandas, as empresas de tecnologia foram obrigadas a desenvolver novos componentes eletrônicos, com maior capacidade de armazenamento, alto desempenho, baixo consumo de energia, comunicação com a internet e ainda reduzir o tempo para produção de suas novas tecnologias. No desenvolvimento de uma arquitetura de uma nova tecnologia a fase de projeto é fundamental, pois levantar todos os requisitos necessários, design e mapeamento dos componentes, analisar o desempenho da arquitetura e, ainda relacionar o custo/benefício para produção ideal é uma corrida contra o tempo. Hoje, existem ferramentas para projetar, testar e analisar o resultado das arquiteturas sem que para isso seja necessário fabrica-las. Isso é muito importante, pois produzir uma única unidade de arquitetura é um custo relativamente alto. No desenvolvimento dessas novas arquiteturas a memória cache se tornou essencial para garantir o alto desempenho do processador. A cache funciona como um pequeno repositório para o processador fornecendo dados e novas instruções de forma rápida e precisa sem usar o barramento do sistema, diminuindo o fluxo de informações no barramento. Dessa forma, o processador trabalha mais e passa menos tempo ocioso. Este trabalho apresenta uma descrição de uma implementação de cache usando uma linguagem para descrever hardware. Este estudo mostra a relação existente entre diferentes tamanhos de cache, comparando estatisticamente a área ocupada da implementação final em uma arquitetura reprogramável.

#### **Abstract**

The companies are looking for ways to improve their business, creating new management models and new services to their clients, that is why the use of new technologies such as: embedded systems, mobile phones and notebook, became essential. Because of the growing of new demands, technology companies were forced to reduce the production time of their new technologies, and develop new electronic components with larger storage capacity, higher performance, lower energy consumption and internet connection. The project phase is an essential step on the development of a new architectures, to evaluate all the necessary requirements, design and components mapping, to analyze the architecture's performance and to evaluate the production's cost/benefit is a race against the time. Nowadays, we have tools to project, test and analyze the architecture's results without manufacturing it. This is very important, because the production of one single unit can be expensive. The cache memory became essential to assure the high performance of processors on the development of these architectures. The cache memory works like a little repository to the processor, supplying data and new instructions in a fast and precise way, without using the system's bus, decreasing the information' stream on the bus. With this, the processor works more often and spend less in idle. This work describe a cache implementation using a hardware language description. This study shows the relation between different sizes of cache, comparing statically the used area of the final implementation in a reprogramable architecture.

## Sumário

| Índice de Figuras                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | v                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Índice de Tabelas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | vi                                                             |

| Tabela de Símbolos e Siglas                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | vii                                                            |

| 1 Introdução                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                             |

| <ul> <li>1.1 Evolução Computacional</li> <li>1.2 Estratégias de Processamento</li> <li>1.3 Objetivos Gerais do Trabalho</li> <li>1.4 Objetivos Específicos do Trabalho</li> </ul>                                                                                                                                                                                                                                                                                                                  | 10<br>10<br>12<br>13                                           |

| 2 Memória Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14                                                             |

| <ul> <li>2.1 Introdução a Hierarquia de Memória</li> <li>2.2 Memória Cache</li> <li>2.2.1 Estrutura Básica de uma Cache</li> <li>2.2.2 Fluxo de Informação na Cache</li> <li>2.2.3 Fluxo de Leitura</li> <li>2.2.4 Fluxo de Escrita</li> <li>2.2.5 Elementos de um Projeto de Cache</li> <li>2.2.6 Função de Mapeamento Direto</li> <li>2.2.7 Função do Mapeamento Associativo</li> <li>2.2.8 Função do Mapeamento Associativo por conjuntos</li> </ul>                                            | 14<br>16<br>16<br>19<br>19<br>20<br>22<br>24<br>25<br>25       |

| 3 Arquiteturas Reconfiguráveis                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26                                                             |

| <ul><li>3.1 Introdução</li><li>3.2 FPGA's</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26<br>27                                                       |

| 4 Descrição da Cache em VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                             |

| <ul> <li>4.1 Idéia e dificuldade inicial</li> <li>4.2 Descrição e modelagem da cache</li> <li>4.2.1 Detalhes da implementação da cache</li> <li>4.3 Simulações da implementação</li> <li>4.3.1 Módulo Decodificador</li> <li>4.3.2 Módulo Comparador</li> <li>4.3.3 Módulo Buffer de Endereço</li> <li>4.3.4 Módulo Buffer de Dados</li> <li>4.3.5 Módulo Array de Dados</li> <li>4.3.6 Módulo Array de Rótulos</li> <li>4.3.7 Módulo Controlador</li> <li>4.4 Estrutura da arquitetura</li> </ul> | 31<br>31<br>32<br>39<br>40<br>41<br>42<br>43<br>47<br>48<br>49 |

| 5 Estudo de Casos e Resultados                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                                                             |

| 5.1 Simulação e mapeamento dos módulos no FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                                                             |

|     |                                            | ESCOLA POLITÉCNICA<br>DE PERNAMBUCO |

|-----|--------------------------------------------|-------------------------------------|

|     |                                            | iv                                  |

| 5.2 | Análise da implementação no FPGA Virtex II | 52                                  |

| 5.3 | Resultados                                 | 54                                  |

| 6 C | onclusão e Trabalhos Futuros               | 57                                  |

| 6.1 | Conclusão                                  | 57                                  |

| 6.2 | Trabalhos futuros                          | 57                                  |

# Índice de Figuras

| Figura 1.  | Evolução das arquiteturas de processador e memória.             | 11 |

|------------|-----------------------------------------------------------------|----|

| Figura 2.  | Hierarquia de memórias.                                         | 15 |

| Figura 3.  | Diagrama de comunicação entre processador e memória.            | 17 |

| Figura 4.  | Componentes físicos da cache                                    | 18 |

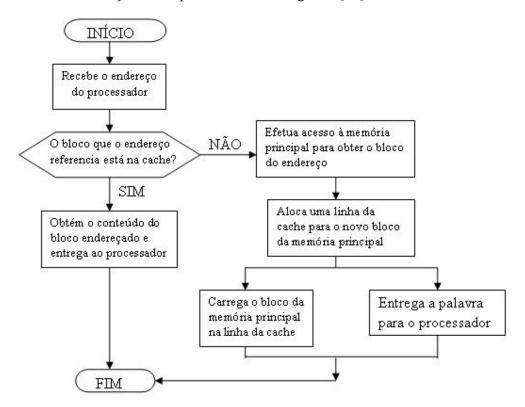

| Figura 5.  | Diagrama de processo de leitura na cache.                       | 20 |

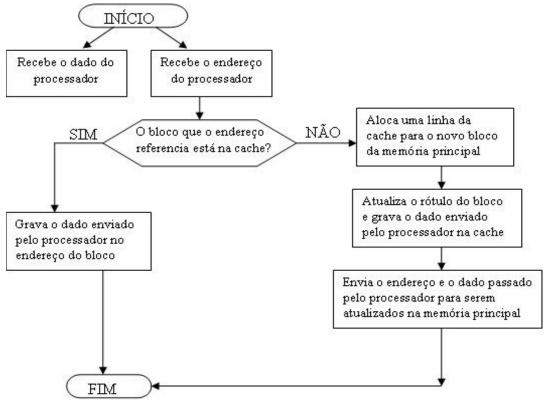

| Figura 6.  | Diagrama de processo de escrita na cache.                       | 21 |

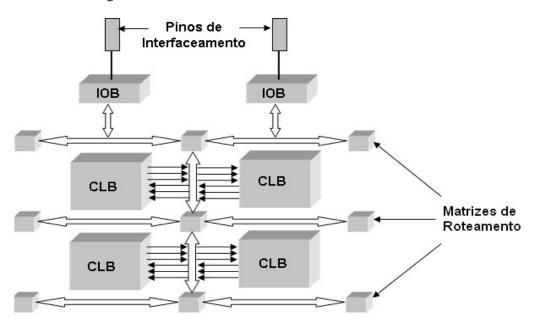

| Figura 7.  | Diagrama de comunicação interna de um FPGA.                     | 28 |

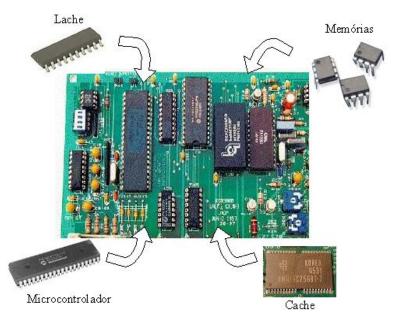

| Figura 8.  | Visualização de um exemplo de placa.                            | 29 |

| Figura 9.  | Ciclo básico de desenvolvimento.                                | 30 |

| Figura 10. | Desenho esquemático da cache.                                   | 33 |

| Figura 11. | Paralelismo de execução – Operação de leitura.                  | 34 |

| Figura 12. | Arquitetura dedicada de cache.                                  | 35 |

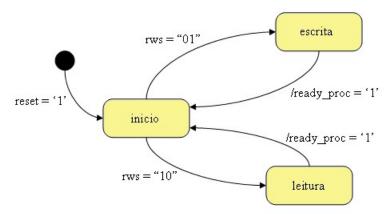

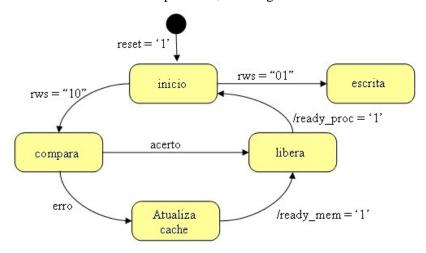

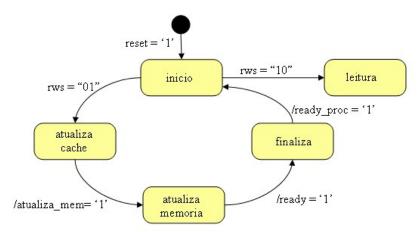

| Figura 13. | Diagrama da máquina de estado do controlador.                   | 37 |

| Figura 14. | Diagrama da máquina de estados – Operação de leitura.           | 38 |

| Figura 15. | Diagrama da máquina de estados – Operação de escrita.           | 39 |

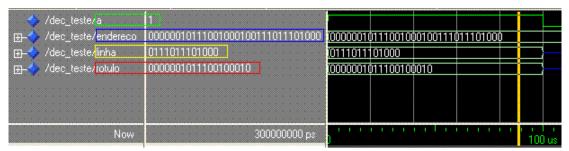

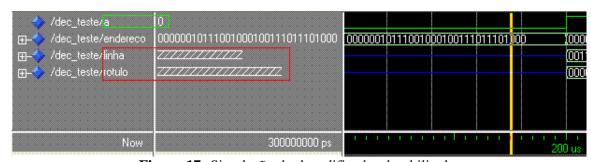

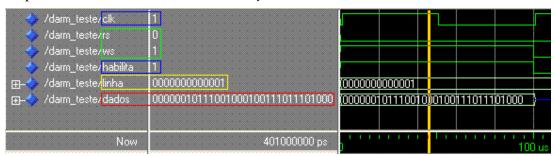

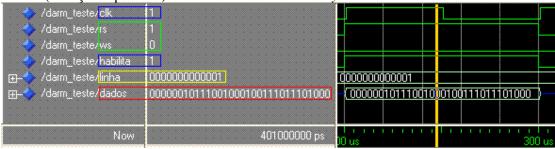

| Figura 16. | Simulação do decodificador habilitado.                          | 41 |

| Figura 17. | Simulação do decodificador desabilitado.                        | 41 |

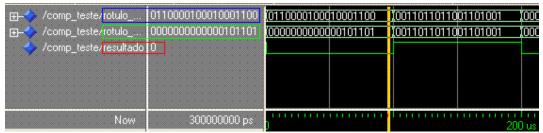

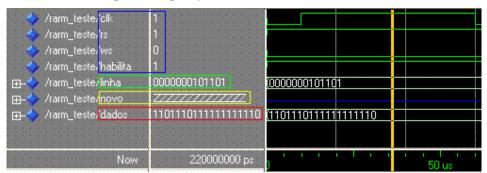

| Figura 18. | Simulação de um erro na comparação.                             | 42 |

| Figura 19. | Simulação de um acerto na comparação.                           | 42 |

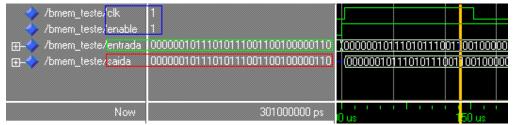

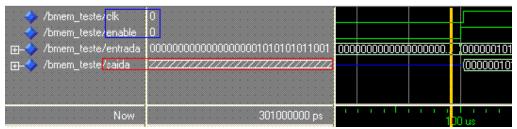

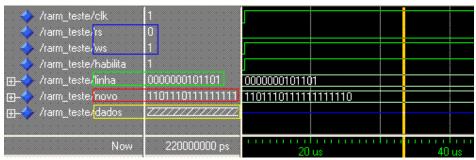

| Figura 20. | Simulação do <i>buffer</i> de memória habilitado.               | 43 |

| Figura 21. | Simulação do <i>buffer</i> de memória desabilitado.             | 43 |

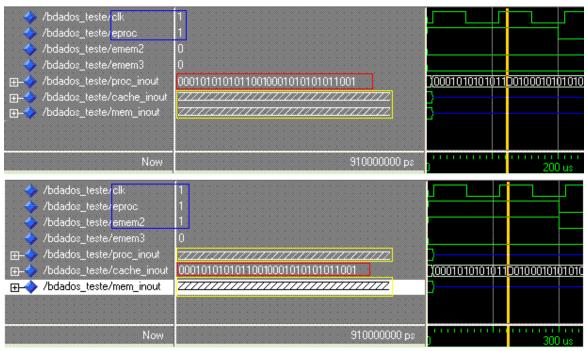

| Figura 22. | Simulações do fluxo <i>buffer</i> de dados e cache.             | 45 |

| Figura 23. | Simulações do fluxo <i>buffer</i> de dados e memória principal. | 46 |

| Figura 24. | Simulação do fluxo da memória principal e buffer de dados.      | 46 |

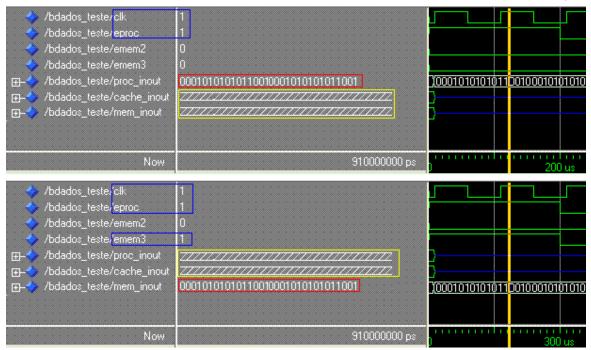

| Figura 25. | Simulação de uma escrita no array de dados.                     | 47 |

| Figura 26. | Simulação de uma leitura no array de dados.                     | 48 |

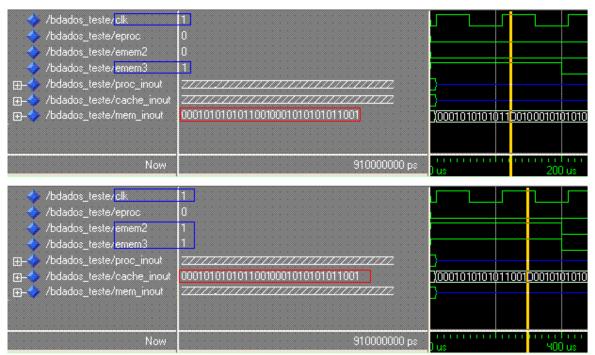

| Figura 27. | Simulação de saída de um rótulo.                                | 48 |

| Figura 28. | Simulação de uma escrita no array de rótulos.                   | 49 |

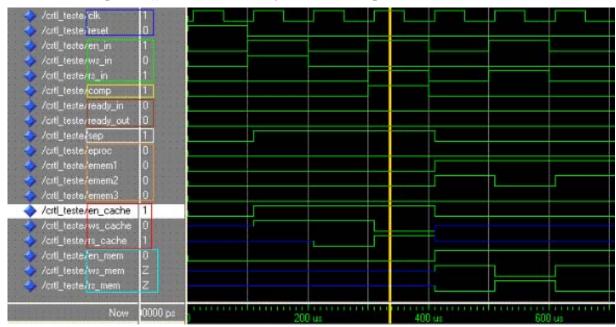

| Figura 29. | Simulação de uma leitura com sucesso na cache.                  | 50 |

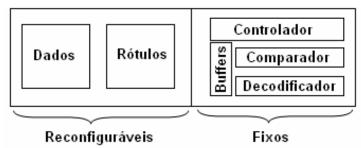

| Figura 30. | Elementos reconfiguráveis da arquitetura de cache.              | 51 |

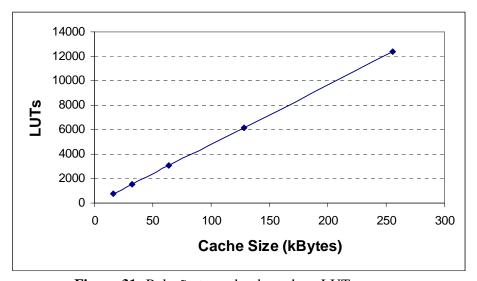

| Figura 31. | Relação tamanho da cache x LUTs.                                | 55 |

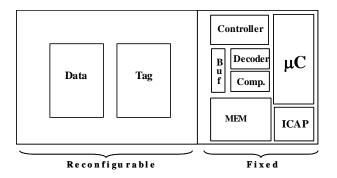

| Figura 32. | Visão dos componentes dentro de um FPGA.                        | 56 |

## Índice de Tabelas

| Tabela 1. Elementos de projeto de uma memória cache.                           | 22 |

|--------------------------------------------------------------------------------|----|

| Tabela 2. Mapeamento de blocos em linhas da cache.                             | 24 |

| Tabela 3. Bits de controle no <i>buffer</i> de dados.                          | 44 |

| Tabela 4. Área percentual dos componentes individuais da cache de 256kbytes.   | 53 |

| Tabela 5. Quantidade de LUTs por dispositivo da família Virtex II da Xilinx.   | 53 |

| Tabela 6. Quantidade de LUTs por tamanho de cache no FPGA da família Virtex II | 54 |

## Tabela de Símbolos e Siglas

(Dispostos por ordem de aparição no texto)

ASIC – Application Specific Integrated Circuit

FPGA – Field Programmable Gate Arrays

VHDL – Very High Speed Integrated Circuit Hardware Description Language

CAD - Computer Aided Design

DRAM – Dynamic Random Access Memory

SRAM – Synchronous Random Access Memory

LRU - Least Recently used

FIFO - First-In-First-Out

LFU - Least Frequently used

ISA - Instruction Set Architecture

CLB – Configuration Logical Blocks (Blocos de Configuração Lógica)

IOB – Input Output Blocks (Blocos de Entrada/Saída)

HDL – *Hardware Description Language* (Linguagem de Descrição de *Hardware*)

RWS – Read-Write Signal (Sinal de controle que determina a operação na cache)

ADL – Architecture Design Language

Dedico esse trabalho a todos os profissionais que contribuem para o surgimento e desenvolvimento de novas tecnologias que auxiliam no progresso humano.

## Agradecimentos

- Gostaria de agradecer a minha família pela dedicação e apoio para que eu me tornasse um profissional de engenharia, em especial a meu pai Nelson Prado e minha mãe Inês Rejane, que foram principais incentivadores e aos meus irmãos que compartilharam dessa minha trilha de algumas tristezas e muitas alegrias;

- Ao professor Abel Guilhermino pela sua dedicação, paciência e sua orientação nos momentos das minhas dificuldades, e hoje, o tenho como amigo;

- Dedico este trabalho aos meus amigos de infância e companheiros de aventuras: Fabrício Fernandes, André Luiz, Diego Lucena, Lucas Coutinho, Ricardo Fernandes e Carlo Moreno;

- Aos amigos que se formaram e que hoje tenho como companheiros de profissão e amigos para toda a vida: Fernando Antônio, Allan Bruno, Adilson Arcoverde, Cláudio Cavalcanti, Gabriel Alves, Gabriel da Luz, Lívia Brito, Laureano Montarroyos, Alcides Bezerra, Diogo Cavalcanti, Tiago Lima, Rafael Bandeira, Rodrigo Cursino, Rodrigo Brayner, Reinaldo Melo, Adélia Carolina, Carolina Baldisseroto, Carolina Matos, Maíra Pachoalino, Bruna Bunzen, Polyana Olegário, Juliana Lima, César Augusto, Pedro Neto, Adriano Nântua, Hilton e Túlio Campos;

- Aos professores do curso de Engenharia da Computação que me ensinaram muitas das coisas que aprendi e por me ensinar a ser um profissional digno e honesto. Agradecimento em especial aos professores Carlos Alexandre, Fernando Buarque, Renato Corrêa, Ricardo Massa, Adriano Lorena e Edson Lisboa.

## Capítulo 1

## Introdução

Neste capítulo, serão abordadas as motivações de fazer este trabalho e também discutir os problemas deste trabalho. Alguns tópicos descritos são relevantes para compreensão deste estudo e serão discutidos no andamento do trabalho.

### 1.1 Evolução Computacional

As empresas estão cada vez mais procurando soluções seguras e rápidas (muitas vezes em tempo real) para os seus empreendimentos e fazem uso das tecnologias emergentes para tal finalidade. A informática e a engenharia têm proporcionado inovações nos modelos de negócios e agregado novos serviços a muitos setores de empresas e em muitos ramos da ciência. A evolução tecnológica, por exemplo, tem influenciado em avanços na medicina como mapeamento genético, processamento de DNA, processamento de imagens raios-X, etc.

Nos últimos anos tem-se observado um aumento gradativo no processamento de dados em todos os campos da ciência. Muitos desses processamentos são bastante complexos e exigem uma grande demanda de recursos, tais como: processador, grande capacidade de armazenamento, transmissão interna e externa de dados, processamento de voz e imagens, segurança de dados, sistemas embutidos e indústrias com segmentos robotizados.

O avanço das arquiteturas de *hardware* gerou uma rápida evolução nos computadores. Segundo Gordon Moore, um dos fundadores da Intel, a capacidade dos processadores dobra a cada 18 meses enquanto os custos dos *chips* permanecem constantes [6]. Os componentes eletrônicos estão cada vez menores e mais baratos, oferecendo máquinas multiprocessadas mais acessíveis e menores, diferentes dos primeiros computadores e *mainframes*, que eram máquinas gigantescas e com elevados custos.

A crescente necessidade de poder de processamento das aplicações criou a exigência de novos conceitos de tecnologia, novas metodologias, novas implementações e inovações nos modelos de arquitetura existentes para que essa demanda de processamento fosse atendida.

### 1.2 Estratégias de Processamento

Desde o ENIAC [1], primeiro computador digital, muitas mudanças aconteceram nas arquiteturas de computadores garantindo um aumento de desempenho. Mudanças simples como uma nova

abordagem no mapeamento dos componentes, implementações diferentes para os barramentos do sistema, acréscimo de registradores, uso de memórias programáveis, o uso de memórias diferentes para instruções e dados, e, mudanças mais complexas como o uso de *pipelines* dentro dos processadores, o uso de memórias caches, uso de co-processadores para cálculos auxiliares e processamento gráfico, têm sido fundamental para evolução dos computadores.

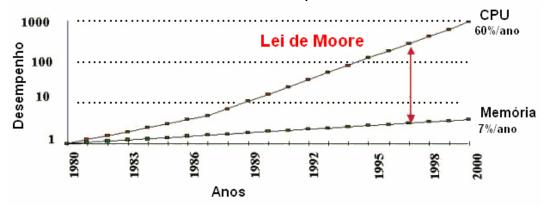

O processador foi um componente que sofreu grande evolução desde a sua primeira concepção, com transistores cada vez menores os chips de computador diminuíram de tamanho e ficaram ainda mais potentes. Mas este alto desempenho do processador não foi acompanhado pelos outros componentes do computador como memórias e dispositivos de entrada/saída, que ficaram mais lentos em relação ao processador no decorrer do tempo [13]. Isso gerou um grande problema, pois o processador com seu alto desempenho passou a ficar ocioso aguardando a comunicação dos outros componentes da arquitetura, ou seja, trabalhava muito rápido, mas tinha ajudantes muito lentos. Na Figura 1 [19] pode se observar a disparidade (segundo a lei de Moore) entre a evolução do processador e a memória, enquanto o processador crescia em média 60% por ano as memórias evoluíam lentamente, em média 7% por ano.

Figura 1. Evolução das arquiteturas de processador e memória.

Muitas das estratégias usadas para melhorar o desempenho do computador foram devidos a esse problema do processador ocioso. Os processadores estavam cada vez mais robustos e rápidos, mas ficavam penalizados devido à ausência de implementações de arquitetura mais eficientes. Para suprir essa necessidade, projetistas de *hardware* criaram novos componentes auxiliares e de controle, e, mudaram muitos conceitos anteriormente implementados. Exemplos disso são as memórias que ficaram cada vez mais rápidas, com blocos diferentes para instruções e dados e novas implementações que permitiram múltiplos acessos às memórias.

Uma das estratégias que teve um grande sucesso na época dos primeiros computadores foi a memória cache, ela aumentava consideravelmente o desempenho do processador. No final década de 80, por exemplo, computadores como o 80486 da Intel trabalhava com um *clock* de 25 MHz e ciclos de 80 ns, mas as memórias mais rápidas da época eram as de 100 ns de atraso, portanto era um tempo de acesso não muito satisfatório [13]. A solução da Intel foi acrescentar ao núcleo do processador uma memória que tivesse um tamanho menor de armazenamento que as memórias existentes (para não aumentar demais a área ocupada pelo processador) e que fosse mais rápida que as memórias convencionais para obter respostas (novas instruções e dados).

O crescimento exponencial da quantidade de transistores para uma mesma unidade de área provocou uma motivação em desenvolver circuitos mais complexos, com mais funcionalidade e integrados em um único chip. Mas a construção de arquiteturas mais complexas ocasionou um aumento no tempo de desenvolvimento dos projetos das empresas. Com isso, ferramentas de desenvolvimento de trabalho são necessárias para conseguir atingir a janela de mercado em

tempo hábil. Desenvolver projetos de maneira rápida passa a ser um desafio para muitas empresas.

Projetar arquiteturas em *hardware* normalmente demora mais tempo para ser concluído quando comparado com projetos de arquiteturas em software. Normalmente projetos desenvolvidos em *hardware* usam linguagens de descrição mais próximas da máquina (ex: VHDL), exigindo muitas vezes experiência e conhecimento dos projetistas. Por outro lado, projetos desenvolvidos em software, normalmente usam linguagens de alto nível (Ex: C e Java) na qual exige, muitas vezes, pouca experiência do projetista.

Uma estratégia para tentar reduzir o tempo de desenvolvimento de projeto é a utilização de ferramentas como as linguagens de descrição de arquitetura (ADL) baseadas em simuladores executáveis, na qual consegue-se emular o comportamento de uma arquitetura que se deseja projetar antes da descrição do *hardware* propriamente dita. Linguagens como ArchC [16], podem servir como suporte para prover ao projetista análises e resultados que façam-no decidir qual a arquitetura adequada para um certo tipo de aplicação.

Existe, hoje no mercado, diferentes abordagens para desenvolvimento de projetos em *hardware*. Dentre essas abordagens, três ganharam muito destaque: ASICs (*Application Specific Integrated Circuit*), Microcontroladores e FPGAs (*Field Programmable Gate Arrays*).

ASICs são circuitos integrados que são fabricados para executar uma tarefa específica. ASICs são utilizados para maximizar o desempenho de uma aplicação ou serviço. As desvantagens dos projetos com ASICs são os elevados custos para fabricação desse componente e a falta de flexibilidade do circuito projetado, uma vez que o ASIC é fabricado, sua lógica interna não pode ser modificada.

Microcontroladores são *chips* têm memórias e interface de entrada/saída integrados e que podem ser programados mais de uma vez. Os microcontroladores são muito utilizados em equipamentos eletrônicos para executar tarefas de controle. A grande vantagem de utilizar microcontroladores no desenvolvimento de uma arquitetura é baixo custo da fabricação em relação aos projetos que contém ASICs.

A terceira abordagem de desenvolvimento são os FPGAs, que são semicondutores digitais que são usados frequentemente para prototipação. Os FPGAs foram concebidos com o intuito de absorver as vantagens existentes nos ASICs e microcontroladores, ou seja, a vantagem de se programar *hardware*, dos ASICs, e a possibilidade da reprogramação existente nos microcontroladores. A grande diferença (e também a grande vantagem) que os FPGAs apresentam em relação as outras duas abordagens vistas, é, a possibilidade de reconfigurabilidade parcial existente nos FPGAs (os detalhes sobre FPGAs serão vistos no capitulo 3), que foi uma das motivações do uso de FPGAs neste trabalho.

A intenção deste trabalho foi acompanhar a evolução das arquiteturas de computadores, principalmente aquelas que se beneficiaram com o uso das memórias caches, e, fazer um estudo aprofundado sobre as caches e suas implementações.

### 1.3 Objetivos Gerais do Trabalho

A idéia do trabalho foi desenvolver uma arquitetura de cache, partindo do conjunto processador/cache/memória, que fornecesse informações suficientes para estudos em arquiteturas reconfiguráveis. Seria desenvolvida uma única arquitetura de cache e a partir desta, variar a capacidade de armazenamento desde modelo para analisar o comportamento da cache em uma arquitetura de FPGA relacionando a área ocupada.

O objetivo deste trabalho é mapear os diferentes tamanhos de cache implementados em uma determinada família de FPGA's com o intuito de encontrar uma relação existente entre a implementação e quantidade de unidades lógicas programáveis (CLB's) dentro de um FPGA.

A conclusão deste trabalho nos motiva a entender que o resultado obtido da área ocupada pelo modelo de cache possa gerar uma equação em termos de unidades lógicas que possa ajudar o projetista a escolher a família de FPGA ideal para o desenvolvimento do projeto.

### 1.4 Objetivos Específicos do Trabalho

A partir da idéia geral, foram especificados os passos seqüenciais para o desenvolvimento do trabalho. A seguir serão descritos os objetivos específicos.

- ✓ Fazer um estudo bibliográfico das arquiteturas de caches existentes no mercado, estudar os métodos de implementação, *design*, comportamento, algoritmos utilizados e benefício (desempenho) que uma cache proporciona em uma arquitetura do computador.

- ✓ Estudar o núcleo do MIPS para compreender a comunicação deste processador com a memória cache e a memória principal. Levantar os dados, as instruções e os sinais de controle que são trocados entre esses componentes.

- ✓ Definir qual a arquitetura de cache a ser implementada em VHDL e determinar, também, a política (tipo de acesso, controle de acesso, algoritmo de atualização) que vai descrever o comportamento da cache.

- ✓ Definir quais os componentes que vão fazer parte da implementação do projeto. Saber a quantidade precisa de componentes para o funcionamento da cache escolhida e determinar a quantidade de sinais para comunicação desses componentes.

- ✓ Implementar em VHDL o modelo específico de cache escolhido com as políticas, sinais de controle e componentes pré-definidos. A partir desse modelo codificado haverá diferentes variações de tamanho na cache para estudos estatísticos da área ocupada.

- ✓ Compilar e simular a implementação da cache através da ferramenta *ISE Foundation* da Xilinx.

- ✓ Analisar os resultados e estudar o impacto da área de FPGA ocupada devido a variação do parâmetro tamanho da cache.

## Capítulo 2

### Memória Cache

Este capítulo aborda os conceitos necessários para compreensão de memórias de computadores. Apresenta uma introdução sobre todos os aspectos de memórias, hierarquias e em específico sobre memórias cache.

### 2.1 Introdução a Hierarquia de Memória

Os sistemas operacionais e programas de computadores estão cada vez maiores e vêem exigindo capacidades ainda maiores de memória e mais rápidas. A memória passou por muitas evoluções desde sua idealização por Von Neumann, onde ele teve a brilhante idéia de unir em um único dispositivo de armazenamento instruções e dados de um programa.

A partir da idéia de Von Neumann, surgiu uma variedade muito grande de memórias e diferentes abordagens de implementação na arquitetura. As diferentes implementações tratavam uma forma de deixar a arquitetura mais eficiente, fazer com que os programas fossem executados mais rápidos. No decorrer do tempo, as memórias ganharam um tempo de acesso quase que instantâneo e ainda pode se observar que o custo por *bit* ficou mais barato.

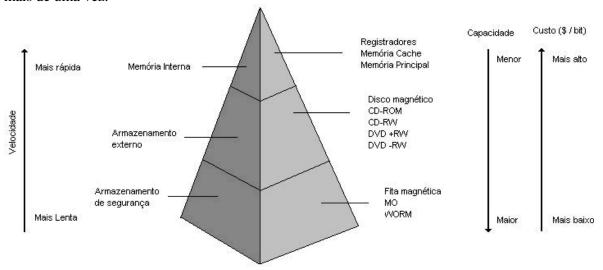

Existem hoje, algumas tecnologias tradicionais de memórias: as SRAM's (memórias de acesso estático), as DRAM's (memórias de acesso dinâmico) e os discos rígidos. As SRAM's são as memórias de menor capacidade e que tem tempo de acesso mais rápido, mas são relativamente mais caras; as DRAM's têm maior capacidade de armazenamento e mais baratas que as SRAM's, mas em compensação são bem mais lentas; e os discos rígidos são dispositivos de grande armazenamento, são mais lentos que as outras memórias e devido a isso tem o custo mais reduzido. A Figura 2 (modificada do livro de Stallings [15]) mostra uma hierarquia de memória relacionando a velocidade, a capacidade de armazenamento e custo por *bit*. Na base estão as memórias com maior capacidade, com menor custo e mais lentas, à medida que avança para o pico da pirâmide as memórias vão ficando mais rápidas, menores e preço por bit vai aumentando.

O ideal da arquitetura é fazer com que as memórias menor de capacidade e mais rápidas trabalhem mais perto do processador, enquanto as memórias de maior capacidade e mais lentas trabalhem indiretamente mais longe do processador [15]. Isto esta associado a um conceito determinado de "princípio da localidade". Imagine que um funcionário esteja trabalhando em uma mecânica e que para executar consertos em um carro precise de uma certa quantidade de ferramentas. A oficina dispõe de todas as ferramentas para conserto de um carro em um único

armário, mas o mecânico não consegue carregar todas as ferramentas ao mesmo tempo e também não quer se dirigir ao armário todas as vezes que precisar de uma ferramenta. Então, o mecânico carrega consigo a quantidade de ferramentas que ele sabe que é necessário para trocar um pneu ou consertar o motor, por exemplo, e dá prioridade as ferramentas que ele sabe que precisará usar mais de uma vez.

Figura 2. Hierarquia de memórias

O princípio da localidade está por trás deste exemplo, ele estabelece que os programas acessem uma parte relativamente pequena do seu espaço de armazenamento em um instante qualquer [13][17], assim como o mecânico que usa uma parte das ferramentas para executar um conserto específico no carro. Existem dois tipos de localidade:

- <u>Localidade temporal</u>: Se um item é acessado, ele tende a ser acessado novamente em um espaço de tempo curto. Se o mecânico do carro usa uma chave de roda para desparafusar uma roda e trocar pelo estepe, existe uma grande chance do mecânico usar a mesma chave de roda para apertar os parafusos após o conserto.

- <u>Localidade espacial</u>: Se um determinado item é acessado, os itens próximos ao item acessado tendem a ser acessados também. Quando o mecânico vai trocar o pneu do carro, ele vai ao armário de ferramentas e pega a chave de roda, mas ele sabe que vai precisar também do braço mecânico (macaco) para levantar o carro e vai usar o mesmo para baixar o carro após trocar o pneu.

As arquiteturas de computadores se utilizam bastante do princípio da localidade, pois como a execução de um programa é seqüencial, existe uma grande probabilidade de que a próxima instrução a ser executada seja a instrução subseqüente. Muitos destes programas executam funções em *loops* fazendo com que a mesma instrução seja executada mais de uma vez, logo, seria extremamente necessário que esta instrução ficasse facilmente disponível.

Nas arquiteturas modernas, as memórias são organizadas hierarquicamente de forma que as memórias mais rápidas fiquem próximas ao processador e contenham informações específicas de um programa, para que estas possam fornecer informações com mais eficiência. As memórias

com maior capacidade ficam mais distantes do processador, atualizando apenas as memórias adjacentes com novos blocos de informação.

No projeto de uma nova arquitetura, o projetista procura relacionar a mais eficiente (mais rápida e precisa) hierarquia de memória com o menor custo de produção, ou seja, o custo/benefício da implementação. As caches são memórias que têm muita influência na hora da implementação de uma arquitetura, elas têm menor capacidade de armazenamento que as memórias principais, são acessadas mais rapidamente, mas em compensação tem o custo muito elevado, por este motivo as arquiteturas não tem somente memórias caches.

A seguir serão discutidos os elementos de projeto que são levados em consideração na construção de uma arquitetura de cache, como: os tipos de mapeamento, algoritmos de substituição, níveis de cache, políticas de escrita, bem como as dificuldades da implementação e os benefícios que ela proporciona à arquitetura de computadores.

### 2.2 Memória Cache

Memórias cache são dispositivos de armazenamento que visam obter uma velocidade mais rápida que as memórias principais e discos rígidos de grande capacidade de armazenamento, mas que possa disponibilizar ainda uma capacidade de armazenamento de dados maior que os bancos de registradores [15].

A rapidez de processamento de dados da cpu é muito alta se comparado com a rapidez da memória principal [13][15]. O processador opera em uma freqüência de ciclos muita alta e necessita de novos dados e novas instruções em um período de tempo muito curto no qual a memória principal não tem condições de acompanhar, pois o tempo de acesso de um dado em uma memória é muito lento. Devido a esse atraso, o processador fica penalizado (ocioso) pela velocidade de fornecimento de informações da memória.

A idéia da memória cache é trabalhar juntamente com a memória principal fornecendo ao processador instruções e dados para execução. A cache contém copias de partes da memória principal e quando o processador requer um novo dado ou uma nova instrução, ao invés de ele solicitar a memória principal, que é relativamente lenta em relação ao processador, ele busca esses novos dados na cache, que é muito mais rápida que a memória principal [13].

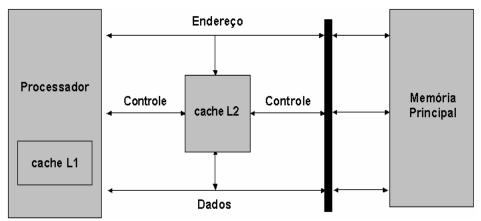

O processador não faz somente busca de instruções e dados na cache, ele também envia dados que são resultados da execução das instruções no processador para que estes possam ser armazenados ou atualizados na memória principal. A Figura 3 [15] mostra um desenho esquemático da cache em uma arquitetura de computador.

#### 2.2.1 Estrutura Básica de uma Cache

A idéia do funcionamento da cache é extremamente simples. Quando um processador vai executar um programa, este movido da memória principal e armazenado total ou parcialmente na cache dependendo do tamanho do programa ou do espaço ainda vazio na cache. Durante a execução de uma instrução do programa, o processador envia para o controlador da cache o endereço referente ou à próxima instrução do programa ou endereço de um dado que seja necessário para alguma operação do processador. Além do endereço, o processador envia ainda sinais de controle que indicam se o endereço passado é para fazer uma busca ou uma escrita na cache (ver Figura 3).

Considerando o processador MIPS, o endereço enviado do processador para a cache é uma palavra de 32 *bits* composta por três campos: rótulo (ou *tag*), *index* e *offset*. O campo *index* é uma seqüência de *bits* que seleciona precisamente qual a linha da cache que se deseja buscar,

neste caso, poderia ser uma nova instrução ou um novo dado. O *offset* funciona como um deslocamento de linha. A cache é composta de várias linhas e cada linha desta pode ter um ou mais blocos de informações (instruções ou dados), o *offset* aponta qual dos blocos, em uma linha, será usado para leitura ou escrita (depende dos sinais de controle).

Figura 3. Diagrama de comunicação entre processador e memória.

Durante o processo de execução de um programa, o processador às vezes executa uma instrução condicional e salta para um outro ponto do programa ao invés de executar a instrução subseqüente, esse desvio condicional do programa traz uma situação inesperada para a cache, pois é muito provável que ela não tenha essa próxima instrução proveniente do desvio e tenha que atualizar um dos seus blocos armazenados por um novo bloco da memória principal.

Na execução de um programa, diferentes partes do programa estão dentro da cache para serem utilizados pelo processador. Quando o processador busca/escreve um novo dado, a cache precisa saber se o dado buscado (ou dado a ser atualizado) ainda esta em um dos blocos da cache. A cache faz uma simples comparação de rótulos para saber se o dado está na sua memória. O rótulo do endereço é uma seqüência de bits que é responsável por essa comparação e que será usado para comparar com o rótulo de uma determinada linha da cache para verificar se a informação buscada (ou que se deseja escrever) está na cache ou não.

A cache é constituída de muitos componentes internos e a sua estrutura básica é composta pelos seguintes componentes:

- Memórias SRAM (RAM Sincronizada): São usadas na cache para armazenar os dados ou as instruções de um programa e também utilizadas para armazenar os rótulos que serão comparados com o rótulo do endereço passado pelo processador.

- <u>Bit de paridade</u>: Cada linha da cache tem um *bit* que funciona como um sinalizador para o controlador, ele serve para indicar a consistência da informação, ou seja, se aquela linha da cache está igual a da memória principal caso contrario o processador saberá que precisa atualizar aquela linha na memória principal.

- Comparadores: São componentes que testam se o rótulo do endereço é igual a algum dos rótulos da cache. Esse teste serve verificar se a informação buscada pelo processador está na cache ou não. O resultado da comparação é um sinal enviado para o controlador indicando que a informação está ou não na cache.

- <u>Multiplexadores</u>: São componentes que recebem diferentes entradas e seleciona uma dessas entradas em uma única saída. Quem indica qual entrada deve ser "jogada" na saída é um sinal de seleção que escolhe uma das entradas. O multiplexador na cache recebe como sinal de seleção o offset e como entrada

recebe os blocos de uma determinada linha da cache. O *offset* selecionará qual o bloco será enviado para a saída ou qual o bloco vai ser atualizado no caso de uma escrita de dados.

- <u>Buffers</u>: São unidades de armazenamento temporário. O *buffer* é bastante utilizado para armazenar temporariamente o endereço passado para cache ou armazenar o dado que se quer ler ou escrever na cache.

- Controlador de cache: É o principal componente da cache. Ele é responsável por todo fluxo da informação e tomada de decisão dentro da cache. O controlador recebe do processador sinais de controle indicando se a operação é de leitura ou escrita e um sinal que habilita/desabilita (ativação) a cache.

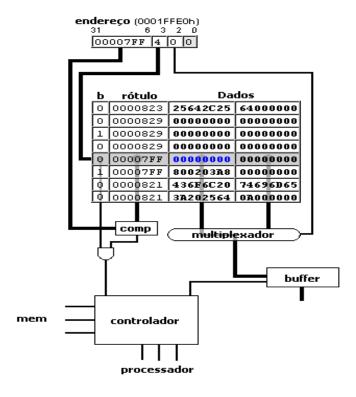

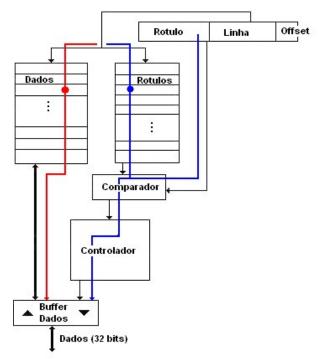

A figura abaixo (modificada do livro de Stallings [15]) ilustra uma cache simplificada com memórias SRAM, para armazenar rótulos, dados e o *bit* de paridade, um comparador, um multiplexador, um *buffer* de armazenamento temporário e o controlador da cache.

Figura 4. Componentes físicos da cache.

Na Figura 4 pode se observar que o endereço enviado pelo processador é dividido em três partes, a primeira parte (rótulo) vai para o comparador para testar se o rótulo do endereço e o rótulo da linha da cache são equivalentes. A segunda é o *index*, que é responsável pela seleção da linha da cache que o processador referenciou. A terceira parte é o *offset* que seleciona quais dos blocos da linha selecionada vai ser enviado para o processador.

#### 2.2.2 Fluxo de Informação na Cache

Durante a execução do processador, dois possíveis fluxos de dados podem ocorrer na cache. Um dos fluxos existente é o de leitura. Durante a execução de um programa o processador faz varias requisições a memória cache atrás de novas instruções ou de novos dados (para terminar uma operação). A cache recebe do processador um endereço de memória que indica qual palavra da cache ele está precisando no momento, caso esta palavra esteja na cache, ela envia esse novo dado para o processador. Pode acontecer do dado desejado não estar presente na cache e o processador precise esperar uma atualização da cache antes de receber o novo dado.

O outro fluxo possível é o de atualização dos dados, o processador após executar uma instrução pode querer gravar os resultados do processamento na memória, neste exemplo o processador além de enviar o endereço de memória, ele também envia o dado a ser armazenado na cache.

Para esses dois fluxos de informações, o que determina se a cache vai executar uma leitura ou uma escrita em suas memórias são os sinais de controle enviados do processador para a cache, estes sinais são emitidos tanto na leitura como na escrita de dados. Nas implementações mais simples de cache, os sinais de controle trocados são três:

- <u>Sinal de Habilitação (Enable EN)</u>: Este sinal (um *bit*) habilita a cache. Quando o processador executa uma instrução que não faz uso das memórias, este sinal é setado para '0' (zero). Quando o processador faz uma leitura ou escrita na cache este sinal é setado para o nível lógico '1' (um) sinalizando a cache que uma operação esta para acontecer.

- <u>Sinal de escrita (Write Signal WS)</u>: Este sinal indica a cache que o processador deseja escrever um dado na memória. O valor que habilita a escrita é '1' (um). Quando o processador deseja atualizar um dado na cache, além de ele enviar um o sinal de habilitação setado para '1' (um), ele envia também o sinal de escrita setado para '1' (um).

- <u>Sinal de leitura (Read Signal RS)</u>: Este sinal indica a cache que o processador deseja fazer uma leitura de um dado armazenado na memória. O valor que habilita a leitura é '1' (um). Quando o processador deseja ler um dado da cache ele envia o sinal de habilitação setado para '1' (um) e o sinal de leitura setado para '1' (um) também.

Em muitas implementações, estes sinais de controle são ativados em nível lógico '0' (zero), isso depende do requisito do projeto. Na implementação desenvolvida nesta monografia, os módulos da cache são ativados quando estes sinais estão em nível lógico alto (um), como descritos acima.

Quando o processador vai fazer uma escrita na cache, ele habilita a cache (*enable* igual a um), seta o sinal de escrita para um, conseqüentemente o sinal de leitura para zero e envia o dado e o endereço onde deve ser armazenada a informação. Quando a requisição é uma leitura, o sinal de escrita vai para zero e o sinal leitura para um, o sinal de habilitação continua em nível alto e o processador envia o endereço referente à palavra a ser buscada.

#### 2.2.3 Fluxo de Leitura

Na seção anterior foi visto quais palavras e quais os sinais que são trocados entre o processador e a memória cache. Durante a execução da CPU, muitas instruções são efetuadas no processamento

e muitos dados são solicitados e atualizados nas memórias. O ciclo de execução de uma leitura de uma instrução é diferente da escrita de dados na cache.

Após o processador enviar o endereço do bloco onde contém a nova instrução, o controlador da cache compara se o rótulo do endereço é igual ao rótulo que está no bloco referenciado, isto é feito porque o processador precisa saber se o endereço que ele queria está na cache ou se o controlador já trocou por outro bloco. Caso os rótulos sejam iguais o controlador da cache acessa o bloco endereçado e envia a informação para o processador. Quando há um acerto na informação buscada se diz que houve um *cache-hit* (acerto).

Quando os rótulos diferem na comparação, o processador aguarda para que o controlador da cache faça uma busca na memória principal, com o mesmo endereço que o processador enviou para a cache, e atualize uma linha da cache (através de escolha) com um novo bloco da memória principal. Essa atualização é feita através de um algoritmo implementado na cache, na seção de elementos de projeto serão apresentados com mais detalhes alguns algoritmos de substituição.

Após o bloco que veio da memória ser atualizado na linha da cache reservada, o controlador da cache envia para o processador a instrução buscada inicialmente. Quando a informação pesquisada pelo processador não está na cache diz-se que houve um *cache-miss* (erro de procura).

O fluxo de execução acima pode ser visto na Figura 5 [15].

Figura 5. Diagrama de processo de leitura na cache.

#### 2.2.4 Fluxo de Escrita

O ciclo de execução da escrita na cache é um pouco mais complexo que o ciclo de leitura. Quando o processador vai atualizar um novo dado, ele precisa saber se o dado desatualizado ainda está armazenado na cache só para depois sobrepor o dado antigo.

O processador envia para a cache além do endereço e sinais de controle, envia também o dado a ser armazenado na cache. O primeiro passo do controlador da cache é verificar se os rótulos do endereço e da linha referenciada pelo processador são iguais, se afirmativo, o controlador atualiza a cache sobrepondo o dado armazenado pelo dado enviado pelo processador. Diferente da leitura a escrita tem uma preocupação a mais, o controlador tem que atualizar a memória principal também, pois como o processador sobrepôs um novo dado, o dado da memória principal está desatualizado causando inconsistência dos dados. Existem diferentes algoritmos que atualizam a memória depois que a cache é atualizada, esses algoritmos serão vistos com mais detalhes na seção de elementos de projeto.

Caso haja um erro na comparação dos rótulos, dois procedimentos podem acontecer: no primeiro o controlador pode reservar um espaço na cache para ser armazenado o dado enviado pelo processador e só depois atualizar a memória. O segundo caso, o controlador da cache pode preferir atualizar a memória principal primeiro e só depois atualizar a cache fazendo uma busca na memória principal e trazendo o bloco novo para cache.

No caso da escrita, acontecendo um *cache-hit* ou *cache-miss* o controlador terá que se preocupar em atualizar os dados da memória principal. Essa atualização depende do algoritmo de substituição dos blocos implementado na cache.

O diagrama descrito na Figura 6 representa um ciclo de escrita na cache, onde pode ser visto o que acontece se ocorrer um *cache-hit* ou *cache-miss*.

**Figura 6.** Diagrama de processo de escrita na cache.

O sucesso da busca na cache é fundamental para um bom desempenho do sistema, uma busca com acerto, leva não mais que dois ciclos de clock para retornar o resultado para o processador, mas quando há um *cache-miss*, uma nova linha da cache tem que ser atualizada com um novo bloco da memória principal, esse processo leva em média de 48 ciclos de clock e

penaliza o *pipeline* em quatro estágios [12], podendo piorar quando a operação é de escrita na cache. Para contornar essa perda de eficiência no sistema, existem vários algoritmos e técnicas de implementação de cache, que serão vistas com mais detalhes na seção a seguir.

#### 2.2.5 Elementos de um Projeto de Cache

Hoje em dia, existem diferentes tipos de tecnologia de cache no mercado, estas caches têm implementações diferentes uma das outras e dependem da necessidade do sistema. Quando uma arquitetura vai ser descrita os projetistas fazem a opção de usar hierarquias de memórias e o uso de cache. Na descrição da cache, alguns elementos de projeto podem ser levados em consideração. A Tabela 1 relaciona elementos básicos de projeto de cache.

Tamanho da memória cacheAlgoritmos de substituiçãoFunção de mapeamentoMenos recentemente usado (LRU)DiretoPrimeiro a chegar primeiro a sair (FIFO)AssociativoMenos freqüentemente usado (LFU)Associativo por conjuntosPolítica de escritaNúmero de memórias cacheEscrita direta (write-throgh)Um ou dois níveisEscrita de volta (write-back)

Tabela1. Elementos de projeto de uma memória cache.

Os elementos mostrados na tabela dizem respeito a:

- Tamanho da cache: Diz respeito à capacidade total de armazenamento da cache. O tamanho da cache deve ser relativamente pequeno, pois o custo por bit da memória cache é muito alto, mas o tamanho deve ser suficiente para que o tempo de acesso seja muito rápido e o numero cache miss seja o menor possível.

- <u>Função de mapeamento</u>: Esta função determina como a cache é organizada. Como o tamanho da cache é menor que a memória principal, é necessária uma função que faça mapeamento dos blocos da memória principal na memória cache e determine quais os blocos da memória principal estão armazenados na cache. As função de mapeamento direto, associativo e associativo por conjuntos vão ser descritos também na seção 2.2.6, 2.2.7 e 2.2.8 respectivamente.

- Algoritmo de substituição: Quando um bloco de cache vai ser atualizado deve existir um algoritmo que determine qual o bloco da cache deve ser retirado para comportar o novo bloco copiado da memória principal. Este algoritmo deve ser implementado em *hardware* para que a velocidade de acesso seja alta. Existem três algoritmos bem difundidos e bastante utilizados, que são:

- Menos recentemente usado (LRU) Este algoritmo substitui o bloco que não é usado há mais tempo no conjunto da cache.

- o Primeiro a Chegar Primeiro a Sair (FIFO) Este algoritmo substitui o bloco que está há mais tempo armazenado na cache.

- o Menos frequentemente usado (LFU) Este algoritmo substitui o bloco da cache que foi menos utilizado.

- <u>Políticas de atualização</u>: são políticas de controle que agem de forma a manter a consistência dos dados. Antes de um bloco da cache ser substituído é preciso verificar se

houve alguma alteração e se esta alteração foi propagada até a memória principal. Se a alteração do bloco foi atualizada na memória principal, este bloco é descartado. Caso a alteração do bloco não tenha sido repassada para a memória, a cache tem que atualizar a memória, só para depois descartar o bloco. Existem três políticas de atualização de cache:

- Escrita direta (write-through) é a técnica mais simples. Toda vez que a cache é atualizada, essa atualização é automaticamente repassada para memória principal. Essa técnica tem um problema crítico, como ela faz atualizações sucessivas, ela pode criar um gargalo no barramento de comunicação do sistema, pois como muitas atualizações estão sendo enviadas para memória principal, elas podem deixar o barramento muito ocupado e fazer com que periféricos que compartilhem o barramento esperem desnecessariamente. Uma solução para esse problema é o uso de buffers auxiliares para armazenar temporariamente os dados que têm que ser atualizados na memória principal e quando houver uma oportunidade repassar os dados do buffers para a memória principal.

- o Escrita de volta (write-back) Essa técnica visa diminuir as atualizações sucessivas da cache. Quando a cache é alterada, um bit de *flag* é setado para '1' (um) indicando que aquela linha da cache sofreu alteração, quando o bloco vai ser descartado a cache verifica as linhas que têm o *bit* indicativo igual a '1' (um) e atualiza estas linhas na memória principal. A desvantagem dessa técnica é que os dados na memória podem ficar desatualizados por muito tempo, pois as linhas da cache só serão atualizadas na memória principal quando houver descarte de algum bloco devido a alguma substituição.

- Número de memórias cache: Com o avanço das tecnologias de cache, novas implementações e protótipos surgiram aumentando o desempenho da cache. Uma dessas novas técnicas foi a possibilidade de inclusão da cache na pastilha do processador, antes externa. Com a cache agora interna (chamada de L1 Level 1), o processador não precisa mais acessar o barramento do sistema para fazer uma consulta na cache, diminuindo o gargalo do sistema e melhorando o tempo de resposta. A desvantagem desse avanço é o fato de que a cache ainda acessa o barramento do sistema para fazer a substituição dos blocos.

Uma nova abordagem foi adicionar uma cache externa (L2 – Level 2) ao sistema. Esta cache externa faz a comunicação com a memória principal e com a cache interna. Existem duas vantagens nesta abordagem: uma é que a cache interna não mais acessa o barramento do sistema, diminuindo o gargalo e a outra vantagem é que o numero de acertos aumentou consideravelmente, pois quando os dados não forem encontrados na cache L1 é bastante provável que eles já estejam na cache L2 [15].

O uso de hierarquia de memórias foi uma evolução nas arquiteturas de *hardware*, ela proveu um melhor desempenho aos computadores que antes sofriam com o lento tempo de resposta, o processador passou a ficar menos tempo ocioso aguardando novas instruções.

As diferentes implementações de hierarquia de memórias e uso de cache dependem da necessidade da arquitetura. Os computadores pessoais, por exemplo, usam caches de tamanho pequeno, pois o fluxo de informação não é tão grande e constante. Já máquinas que são usadas como servidores em empresas, são máquinas robustas e têm fluxo (quantidade) de informações muito grande e constante, precisando de um tempo de resposta eficiente, por isso as arquiteturas dessas máquinas são compostas de processadores poderosos e caches de tamanho grande, elevando o custo do computador.

Toda nova arquitetura que vai ser desenvolvida passa por uma fase de projeto demorada e minuciosa, pois os projetistas tentam ajustar os componentes de acordo com a finalidade da

implementação. Os projetistas precisam testar a placa antes do processo de fabricação, porque fabricar uma única peça tem um custo muito elevado e não justifica os gastos.

#### 2.2.6 Função de Mapeamento Direto

Nesta seção será descrita a função de mapeamento direto. Esta explanação será muito útil brevemente, pois a implementação desenvolvida neste trabalho usa mapeamento direto como função de preenchimento da cache.

A função de mapeamento direto é simples e tem baixo custo de implementação [15]. Nessa técnica, cada bloco da memória principal é mapeado em uma única linha da cache. O endereço enviado pelo processador é usado como referência nesta técnica.

A memória cache tem um tamanho muito menor (em *kbytes*) que a memória principal e precisa de uma função para mapear diferentes blocos da memória em linhas da cache. A idéia do mapeamento direto é associar blocos da memória a posições fixas na cache usando uma equação (1). A função módulo é expressa segundo:

"

$$i = j \text{ m\'odulo m"}$$

(1)

onde 'i' é igual ao número da linha da cache (onde o bloco vai ser armazenado), 'j' é igual ao número do bloco da memória principal e 'm' é a quantidade de linhas da cache. Por exemplo, digamos que haja uma memória principal com duzentos blocos e uma cache com dez linhas para armazenamento, e, que se queira mapear os blocos desta memória principal nas dez linhas da cache. O bloco 0 (zero) ficaria mapeado (segundo a equação) da seguinte maneira, i = 0 mod 10, que é igual a zero, logo o bloco 0 da memória principal ficaria na primeira linha da cache (linha zero), o bloco 56 seria i = 56 mod 10, que é igual a 6, logo o bloco seria mapeado na linha seis da cache (sétima posição) e assim sucessivamente.

A Tabela 2 demonstra o mapeamento completo deste exemplo (m=10 e j=200). A primeira coluna da tabela mostra as linhas da cache, a segunda coluna mostra os blocos mapeados por linha seguindo a equação vista anteriormente e a terceira mostra os diferentes blocos mapeados por linha se baseando na equação. É importante observar que uma mesma linha da cache fica reservada a diferentes blocos, veja que a primeira linha esta reservada para receber os blocos 0, 10, 20, 30,..., 70,..., 120,..., 190, 200, ou seja, todos os blocos que calculados pela equação tem como resultado (resto) zero.

Tabela 2. Mapeamento de blocos em linhas da cache.

| Li | inha da memória cache | Blocos mapeados por linha | Blocos de exemplo         |

|----|-----------------------|---------------------------|---------------------------|

| 0  | 0                     | 0, m, 2m, 3m,             | 0, 10, 20, 30,, 190, 200. |

| 1  | 1                     | 1, m+1, 2m+1, 3m+1,       | 1, 11, 21, 31,, 181, 191. |

| 2  | 2                     | 2, m+2, 2m+2, 3m+2,       | 2, 12, 22, 32,, 182, 192. |

|    | •                     | •                         | •                         |

|    | •                     | •                         | •                         |

|    | •                     | •                         | •                         |

| 8  | m-2                   | m-2, 2m-2, 3m-2, 4m-2,    | 8, 18, 28, 38,, 188, 198. |

| 9  | m-1                   | m-1, 2m-1, 3m-1, 4m-1,    | 9, 19, 29, 39,, 189, 199. |

O mapeamento direto tem a vantagem de ser uma implementação simples e de custo de projeto baixo. A principal desvantagem deste tipo de mapeamento é que diferentes linhas da memória principal estão mapeadas na mesma linha da cache e isso pode trazer um problema grave. Dessa maneira, se o processador estiver executando instruções distintas, mas que estão

mapeadas na mesma linha da cache (ex. instruções 10, 20, 30, etc), o controlador da cache terá que trocar a mesma linha a cada nova instrução causando um grande atraso devido às atualizações dos blocos.

#### 2.2.7 Função do Mapeamento Associativo

A idéia mapeamento associativo é evitar a desvantagem do mapeamento direto, que mapeia cada bloco da memória principal em uma única linha da cache. A vantagem do mapeamento associativo é que qualquer bloco memória principal pode ser mapeado em qualquer linha da cache, desse modo, o endereço enviado do processador é reconhecido como um endereço contendo apenas o rótulo (para comparação) e o dado (informação).

O rótulo é armazenado juntamente com o dado na mesma linha da cache. Quando o processador envia um novo endereço, o controlador compara (ao mesmo tempo) todos os rótulos presentes na cache com o rótulo do endereço enviado, se a informação desejada estiver na cache o controlador envia o dado para o processador, caso contrário um novo bloco da memória principal deverá substituir um dos blocos da cache.

A desvantagem desse mapeamento está justamente no módulo comparador, pois o conjunto de circuitos que são necessários para comparar todos os rótulos em paralelo são muito complexos.

A grande vantagem desse mapeamento é a flexibilidade de carregar um bloco da memória em qualquer posição da cache, dessa maneira, pode-se utilizar um bom algoritmo de substituição para maximizar a quantidade de acertos na cache.

#### 2.2.8 Função do Mapeamento Associativo por conjuntos

O mapeamento associativo por conjuntos aproveita as vantagens do mapeamento direto e associativo e atenua as desvantagens. A idéia desse mapeamento é dividir a cache em diversos conjunto, e cada conjunto desse com uma certa quantidade de linhas.

O controlador da cache, identifica o endereço enviado pelo processador como constituído de três campos: rótulo, conjunto e palavra. O campo rótulo, como nos outros mapeamentos, é utilizado para verificar se a informação desejada pelo processador está na cache ou não, através de uma comparação. Os *bits* que compõe o campo conjunto são utilizados para selecionar um dos conjuntos existentes na cache. Diferente do mapeamento completamente associativo, que compara o rótulo do endereço com todos os rótulos existentes na cache, o mapeamento associativo por conjuntos faz a comparação somente com os rótulos existentes em um único conjunto, que foi selecionado pelo campo conjunto do endereço enviado pelo processador.

A idéia do mapeamento associativo por conjuntos é unir diferentes blocos da memória principal em conjuntos dentro cache. A lógica de controlador é quando receber um novo endereço do processador, selecionar primeiro um dos conjuntos da cache, comparar os rótulos existentes dentro desse conjunto com o rótulo do endereço para obter um dos blocos e selecionar a linha que deve ser retornada para o processador. A taxa de acerto do mapeamento associativo por conjuntos é significativamente maior que os mapeamentos direto e completamente associativo [15].

O projeto desenvolvido nesta monografia usa mapeamento direto porque é mais simples e mais rápido de codificar do que os outros tipos de mapeamento (associativo e associativo por conjuntos). A implementação deste trabalho não visa alcançar um ótimo desempenho nem avaliar os mapeamento e algoritmos existentes, o propósito desta monografia é avaliar o impacto de área, dentro de um FPGA, causado por diferentes tamanhos da cache.

A seguir será introduzido os conceitos básicos e usos mais comuns de arquiteturas reconfiguráveis.

## Capítulo 3

## Arquiteturas Reconfiguráveis

### 3.1 Introdução

A evolução dos computadores proporcionou um beneficio muito grande para o homem, as novas tecnologias inventadas são usadas de formas diferentes em muitos setores da sociedade, gerando novas oportunidades e melhorando a qualidade de vida. Os computadores atuais são frutos de muito estudo e esforço de cientistas de todo o mundo, muitas dessas novas arquiteturas são só possíveis devido a anos de sacrifício em pesquisas exploratórias.

No desenvolvimento de uma nova arquitetura de computador existem muitas fases de projeto como: pesquisas, levantamento de requisitos, estimativas de custos e tempo, codificação, síntese, simulação, testes e só depois os projetistas passam para a fase final de fabricação.

Os projetos de arquitetura, hoje em dia, visam diminuir o tempo de resposta do sistema, melhorar o desempenho, diminuir a dissipação de potência, agregar novas tecnologias a arquiteturas antigas e ainda estimar o custo/benefício de cada máquina. Para isto, novas abordagens de processamento estão sendo estudadas e projetadas a exemplo do processamento paralelo (tanto em nível de *software* como em nível de *hardware*), *grids*, *clusters*, FPGA's, processadores quânticos e nanotecnologias.

Muitas das soluções podem ser concebidas tão somente por *software* quanto por *hardware* ou ainda apresentar um híbrido dessas abordagens. Um dos grandes problemas na construção de sistemas é justamente saber qual paradigma usar para o seu desenvolvimento. As implementações por *software* ou *hardware* apresentam algumas vantagens e desvantagens relacionadas ao desempenho, flexibilidade e principalmente ao custo.

As implementações por software têm a vantagem de ser bastante flexíveis, ou seja, no decorrer do desenvolvimento do sistema podem ocorrer mudanças no projeto que alterem algum requisito ou codificação do *software*; e ainda apresentam a vantagem de ser soluções mais baratas do que as soluções em *hardware*. A principal desvantagem das implementações em *software* é o fato destas apresentarem um desempenho, muitas vezes, insatisfatório nas suas aplicações.

A implementação por *hardware* tem a vantagem do alto poder de processamento, pois suas funções são implementadas em baixo nível e suas instruções estão bem formatadas para processamento. Mas desenvolver soluções em *hardware* são caras (alto custo na produção), demandam muito tempo de simulação e uma vez produzidas não podem mais ser alteradas. Muitas das soluções em *hardware* são para um propósito específico e não podem ser utilizadas

para outras aplicações, sub-utilizando esta implementação. As construções baseadas em *hardware* são muito indicadas para processamento especifico ou implementação de sistemas que exijam alto processamento, respostas precisas e rápidas.

As desvantagens desses paradigmas apresentados (*software* e *hardware*) causaram uma necessidade de desenvolver novos modelos e implementações computacionais, desse modo, originou-se um novo modelo computacional chamado de computação reconfigurável. Esses sistemas tentam implementar soluções intermediárias entre os modelos de *hardware* e *software*.

Diferente dos microprocessadores que executam programas de forma seqüencial, as arquiteturas reconfiguráveis têm a vantagem de executar programas paralelamente, pois os chips são fabricados com várias unidades programáveis que se comunicam através de vias; cada uma destas unidades pode implementar diferentes tipos de circuitos integrados e podem ser usados independentemente um dos outros, muitas vezes aumentando o poder de processamento.

A base das arquiteturas reconfiguráveis é componente eletrônico reprogramável chamado FGPA, que é na verdade um conjunto de blocos lógicos interligados por vias e unidades de roteamento. FPGA será discutido com mais detalhes na próxima seção.

#### 3.2 FPGA's

A computação reconfigurável tem o intuito de diminuir o espaço existente entre os paradigmas de *hardware* e *software*, possibilitando aos projetistas de computadores uma nova visão de desenvolvimento[8]. Apesar da computação reconfigurável ser bastante recente e seus conceitos ainda não estarem firmados [9], essa tecnologia permitiu a implementação em nível de *hardware*, mantendo o alto desempenho das implementações, e agora também com uma flexibilidade que antes não existia.

Arquitetura de FPGA's permitem que estruturas internas programáveis sofram reconfigurações diferentes da original, durante a execução (ou após o termino de uma tarefa, ou ainda parte dela) de um programa de acordo com a necessidade do usuário [9]. É importante frisar que isto só é possível quando se tem em mãos uma arquitetura de FPGA's que suporte reconfiguração dinâmica parcial. Com bons olhos nessa característica de reconfiguração e partindo da idéia que o intervalo de aplicações também aumenta quando se usa uma arquitetura destas, vamos nos ater a explorar a arquitetura de FPGA's do fabricante Xilinx [18] que possui esta característica.

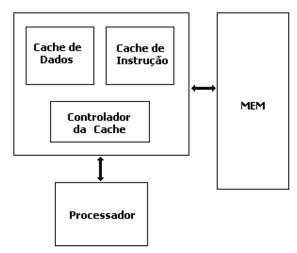

Os chips reprogramáveis (FPGA) da Xilinx são constituídos de três elementos de configuração: blocos lógicos programáveis (*CLB*), circuitos de interfaceamento e vias de interconexões, esses elementos podem ser melhores ilustrados na Figura 10.

Os CLB's são circuitos constituídos de flip-flops e lógica combinacional, que podem trabalhar isoladamente ou em conjunto, através de interconexões. Um único FPGA contém vários CLB's idênticos que podem ser programados de forma diferente, tanto pelo projetista como pelo usuário, para ser adequar a necessidade do programa. A programação do FPGA e a configuração das vias podem ser feitas estática ou dinamicamente, ou seja, a programação dos componentes internos do *chip* podem ser feitas antes da execução das tarefas de um programa ou podem acontecer durante a execução das tarefas. O projetista (ou usuário) pode ainda reconfigurar (de forma estática ou dinâmica) uma conexão existente entre CLB's e fazer com que certas unidades não se comuniquem entre si e passem a se comunicar com outras unidades com as quais não se comunicavam.

Os circuitos de interfaceamento, também chamados de IOB's (*Input Output Blocks*) são buffers bidirecionais com saídas em alta impedância, que fazem a comunicação do FPGA com os demais componentes do computador. Esses pinos podem ser configurados para funcionar

somente como entrada do FPGA quando outros componentes da placa enviam dados para serem processados internamente, e, podem ser programados somente como pinos de saída quando o FPGA envia dados para outros componentes ou ainda podem ser configurados como bidirecionais quando o FPGA está se comunicando nas duas direções ao mesmo tempo.

Existem ainda no FGPA as vias de interconexões, que são grupos de trilhas que fazem as conexões entre as CLB's, comunicando suas entradas e saídas e também fazem a comunicação com os circuitos de interfaceamento. A programação destas interconexões é chamada de roteamento e geralmente são programadas internamente por células que determinam as funções de roteamento, indicando quais CLB's estão se comunicando e através de quais trilhas se comunicam com IOB's. Todas as vias internas são constituídas de segmentos metálicos que suportam chaveamento, desta maneira pode-se programar o destino desejado da comunicação.

A Figura 7 [9] mostra um diagrama representativo de um FPGA da Xilinx, as interconexões e a configuração dos pinos do FPGA podem ser alteradas durante a execução dos programas, bem como a lógica interna de cada CLB.

**Figura 7.** Diagrama de comunicação interna de um FPGA.

As primeiras arquiteturas eram projetadas e fabricadas com núcleos independentes e com circuitaria fixa. Cada um dos componentes eram programados e fabricados antes de serem agregados com a arquitetura final, esses componentes podiam ser programados por empresas diferentes de *hardware*, dessa forma o fabricante da arquitetura se abstraía da lógica interna de cada componente. A desvantagem desse tipo de desenvolvimento é que se um componente tivesse que ser alterado, por necessidade de requisito, ele tinha que ser produzido novamente agregando novos custos ao projeto. Através da Figura 8 pode se visualizar o método de desenvolvimento das primeiras arquiteturas, onde os chips são produzidos separadamente e soldados na arquitetura final.

A programação dos componentes internos do FPGA como memórias, registradores, microcontrolador, cache, *buffers* e toda configuração de CLB's, IOB's e matrizes de roteamento é feito de forma diferente das arquiteturas fixas. Ao invés dos componentes serem pré-fabricados independentemente para serem colocados na placa, eles são desenvolvidos, estruturados e são sintetizados em string de bits para serem carregados dentro do FPGA. As implementações dos

componentes podem ser feitas com ferramentas de descrição de *hardware* como o *Foundation*, da Xilinx, ou o Max Plus II da Altera.

Figura 8. Visualização de um exemplo de placa.

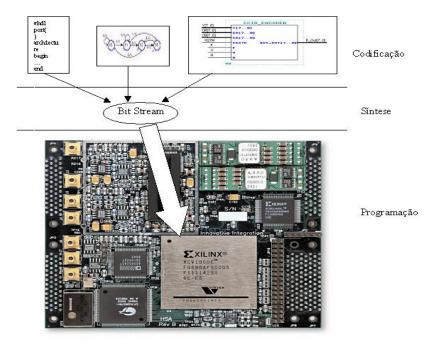

A Figura 9 mostra um exemplo de desenvolvimento de uma arquitetura usando FPGA, desde a sua concepção até a programação dos CLB's, IOB's e matrizes de roteamento. A primeira etapa é implementar os arquivos dos componentes e compilá-los sintaticamente, a segunda fase é a de sintetização dos arquivos gerados em *string* de *bits* para armazenar no FPGA e a fase final é programar as unidades do FPGA para receber os arquivos sintetizados.

As arquiteturas reprogramáveis apresentam algumas vantagens sobre as arquiteturas fixas com relação ao custo e reutilização. Construir arquiteturas usando FGPA tem um custo relativamente mais barato, pois muitos dos componentes necessários para a arquitetura não precisam ser fabricados porque eles podem ser codificados e sintetizados dentro do FPGA, o único custo empregado seria pagar pelo desenvolvimento dos *cores* (circuito lógico) do componente que serão utilizados dentro do FPGA [3]. Uma outra vantagem é a reprogramação, dinâmica ou estática, do FPGA. O programador ou usuário pode reutilizar o FPGA para outras aplicações, precisando somente baixar novos *cores* para o FPGA e programar novamente as unidades de roteamento e os pinos de interfaceamento.

As únicas desvantagens são o tempo de resposta e a complexidade de programação do FPGA. O desempenho do FPGA é mais lento do que nas arquiteturas fixas porque existem muitos circuitos lógicos se interligando dentro do FPGA, por isso os atrasos dos pulsos elétricos são maiores que nos componentes dedicados das arquiteturas fixas. Como o FPGA suporta uma grande quantidade de circuitos internos, a programação das matrizes de roteamento e pinos de entrada/saída se tornam muito complexas, pois os blocos lógicos precisam ser interligados internamente e os componentes do FGPA precisam se comunicar com os dispositivos externos.

Figura 9. Ciclo básico de desenvolvimento.

Para facilitar o projeto de desenvolvimento de novas placas e arquiteturas são utilizadas ferramentas CAD (*Computer Aided Design*), que são ferramentas que ajudam no desenvolvimento do projeto, pois elas disponibilizam toda a estrutura necessária para implementação de uma arquitetura como: design da arquitetura, ambiente de codificação, compilação da sintaxe, simulação dos componentes (isolados ou projeto final), geram relatórios de dissipação de energia e desempenho, fazem mapeamento dos circuitos lógicos implementados dentro do FGPA e ainda fazem programação automática das matrizes de roteamento.

## Capítulo 4

## Descrição da Cache em VHDL

Nos capítulos anteriores tentou-se expor o estado da arte dos temas abordados neste trabalho, bem como explicar os detalhes necessários para compreensão do mesmo. Com a base teórica findada, espera-se agora demonstrar os aspectos práticos deste trabalho e que as informações obtidas com os resultados alcançados, sirva para ajudar no desenvolvimento de projetos novas arquiteturas de *hardware*.

A apresentação da metodologia objetiva demonstrar os aspectos práticos implementados e as simulações executadas neste trabalho

#### 4.1 Idéia e dificuldade inicial

No capitulo 2, foram discutidos os componentes da cache, suas implementações e os aspectos de projeto que influenciam no desenvolvimento. Neste capítulo, será discutida a implementação da cache feita pelo autor, bem como as dificuldades do desenvolvimento e a escolha da cache a ser desenvolvida.

A modelo de cache implementado foi baseado em estudos sobre arquiteturas de cache existentes [15]. O intuito deste trabalho não foi desenvolver novos tipos de mapeamento e algoritmos de substituição da cache, a idéia foi codificar um modelo de cache existente usando a linguagem de descrição VHDL.

A idéia inicial era fazer uma cache parametrizável onde um usuário pudesse configurar a cache em termos de capacidade de armazenamento, tipo de mapeamento (direto, associativo, associativo por conjunto) e o algoritmo de substituição.

Uma cache totalmente parametrizável era um projeto que gastaria muito tempo de implementação e não caberia no escopo deste trabalho. Foi preciso então definir um escopo de projeto menor de cache para desenvolver.

### 4.2 Descrição e modelagem da cache

A arquitetura de cache a ser modelada foi selecionada aleatoriamente baseada nos estudos e implementações iniciais. As implementações iniciais sofrearam bastantes modificações devido à dificuldade, induzindo a uma escolha de projeto com uma complexidade menor.

O projeto da cache produzido é baseado na Figura 4 vista anteriormente. Neste modelo pode ser visto a memória que armazena as informações (bit de paridade, dados e rótulos), o módulo comparador que sinaliza se a palavra esta no banco de informações, o multiplexador que seleciona o bloco da linha que será enviado (ou atualizado) para o processador, o *buffer* de dados que armazena temporariamente o dado da cache e o módulo controlador que é responsável por todo o fluxo dentro da cache.

A arquitetura de cache definida e implementada é muito parecida com a descrita anteriormente, com algumas particularidades. Por exemplo, a memória foi separada em memória de dados e memória de rótulos para facilitar a comparação, foi implementado um módulo decodificador, foi acrescido um *buffer* para armazenamento temporário do endereço da instrução e sinais de controle. Os detalhes e a definição dos componentes serão vistos na próxima seção.

#### 4.2.1 Detalhes da implementação da cache

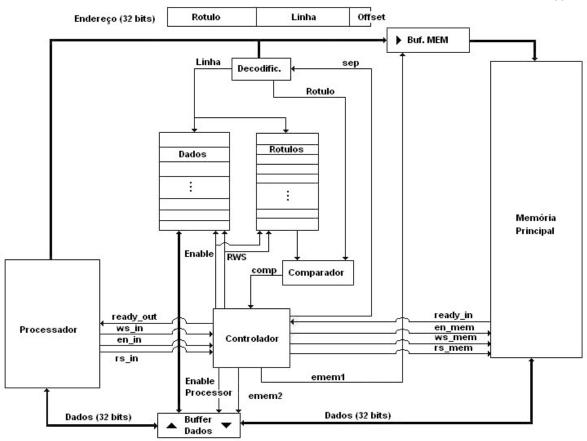

O desenho esquemático representado na Figura 10 foi essencial para compreensão da implementação. Os estudos relacionados a arquiteturas de cache foram muito trabalhosos, porque muitas das literaturas sobre organização de computadores abordam sobre o funcionamento da cache, seus algoritmos, desempenho, custos, estatísticas, detalhes de projeto, mas não explica a implementação física dos componentes em um nível lógico mais baixo que seria de muita utilidade para o projeto deste trabalho.

O artigo de Mamidipaka e Dutt [7], foi um dos poucos lidos que descrevia em nível de detalhes os principais componentes de uma arquitetura de cache. Este artigo foi fundamental para o entendimento do projeto, para esclarecer algumas idéias e ajustar a descrição final do trabalho antes de partir para implementação.

O projeto final da arquitetura da cache ficou definido da seguinte maneira (ver Figura 10): um módulo decodificador, um comparador de *bits*, dois *buffers* de armazenamento temporário (um *buffer* para armazenar dados e outro para armazenar um endereço), um banco de armazenamento para guardar dados e instruções, outro banco para armazenar rótulos identificadores de linha e o módulo cérebro da cache, o controlador.